1<sup>st</sup> class Dr. Rasim Azeez

### **Decoder**

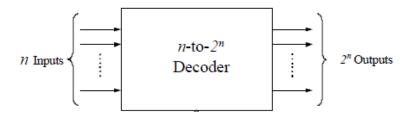

As its name indicates, a decoder is a circuit component that decodes an input code. Given a binary code of n-bits, a decoder will tell which code is this out of the  $2^n$  possible codes (See Figure ). Thus, a decoder has n- inputs and  $2^n$  outputs. Each of the  $2^n$  outputs corresponds to one of the possible  $2^n$  input combinations.

In general, output i equals 1 if and only if the input binary code has a value of i.

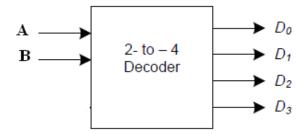

#### Example: 2-to-4 decoder

Let us discuss the operation and combinational circuit design of a decoder by taking the specific example of a 2-to-4 decoder. It contains two inputs denoted by A and B and four outputs denoted by D0, D1, D2, and D3 as shown in figure.

Figure Block Diagram of 2-to-4 Decoder

| В | A | D <sub>0</sub> | $D_1$ | <i>D</i> <sub>2</sub> | <i>D</i> <sub>3</sub> |  |

|---|---|----------------|-------|-----------------------|-----------------------|--|

|   |   |                | ,     |                       |                       |  |

| 0 | 0 | 1              | 0     | 0                     | 0                     |  |

| 0 | 1 | 0              | 1     | 0                     | 0                     |  |

| 1 | 0 | 0              | 0     | 1                     | 0                     |  |

| 1 | 1 | 0              | 0     | 0                     | 1                     |  |

Truth table of 2-to-4 Decoder

As we see in the truth table, for each input combination, one output line is activated, that is, the output line corresponding to the input combination becomes 1, while other lines remain inactive. For example, an input of 00 at the input will activate line  $D_0$ , and 01 at the input will activate line  $D_1$ , and so on.

<u>1<sup>st</sup> class</u> Dr. Rasim Azeez

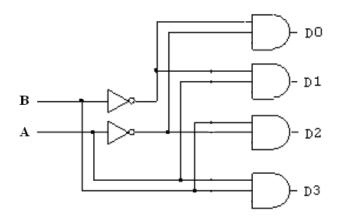

$$D_0 = \overline{A}\overline{B}$$

$$D_1 = A\overline{B}$$

$$D_2 = \overline{A}B$$

$$D_3 = AB$$

The logic diagram of 2-to- 4 Decoder

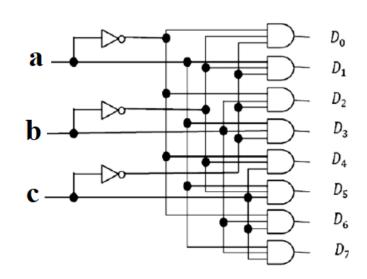

### Example: 3-to-8 decoder

It contains three inputs denoted by a, b and c, with eight outputs denoted by D0, D1, D2, D3, D4, D5, D6 and D7 as shown in figure

| С | b | а | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 |

|---|---|---|----|----|----|----|----|----|----|----|

| 0 | 0 | 0 | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0 | 0 | 1 | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0 | 1 | 0 | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  |

| 0 | 1 | 1 | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| 1 | 0 | 0 | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

| 1 | 0 | 1 | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 1 | 1 | 0 | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 1 | 1 | 1 | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

$$D_0 = \overline{c}\overline{b}\overline{a}$$

$D_1 = \overline{c}\overline{b}a$

$D_2 = \overline{c}b\overline{a}$

$D_3 = \overline{c}ba$

$D_4 = c\overline{b}\overline{a}$

$D_5 = c\overline{b}a$

$D_6 = cb\overline{a}$

$D_7 = c\overline{b}a$

1<sup>st</sup> class Dr. Rasim Azeez

## **Encoder**

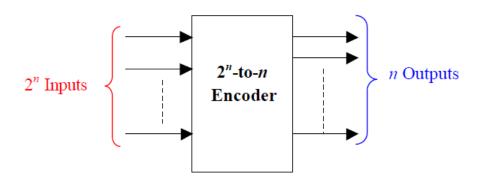

The encoder is a combinational circuit that performs the reverse operation of the decoder. The encoder has a maximum of  $2^n$  inputs and n outputs. Only one input can be logic 1 at any given time (active input). All other inputs must be 0's.and the Output lines generate the binary code corresponding to the active input. The block diagram of  $2^n$  –to-n encoder as shown below.

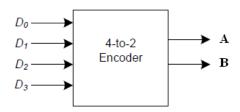

### **Example: 4-to-2 Encoder**

The inputs are 4 and the outputs are 2

The block diagram and the truth table of a 4-to-2 encoder are shown below.

Figure Block Diagram of 4-to-2 Encoder

| $D_0$ | $D_1$ | $D_2$ | D <sub>3</sub> | В | $\mathbf{A}$ |

|-------|-------|-------|----------------|---|--------------|

| 1     | 0     | 0     | 0              | 0 | 0            |

| 0     | 1     | 0     | 0              | 0 | 1            |

| 0     | 0     | 1     | 0              | 1 | 0            |

| 0     | 0     | 0     | 1              | 1 | 1            |

truth table For the 4-to-2 encoder

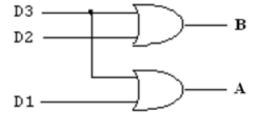

So that the logic expression of outputs are:

$\mathbf{A} = \mathbf{D1} + \mathbf{D3}$

B = D2 + D3

And the logic diagram of 4-to- 2 encoder as shown below:

Logic Diagram of the 4-to-2 Encoder

1<sup>st</sup> class Dr. Rasim Azeez

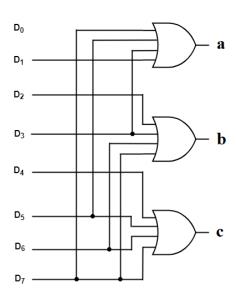

### **Example: 8-to-3 Encoder**

The inputs are 8 and the outputs are 3. The truth table and the logic diagram of a 8-to-3 encoder are shown below.

|   |    | INPUTS |    |    |    |    |    |    |   | UTPUT | S |

|---|----|--------|----|----|----|----|----|----|---|-------|---|

|   | D0 | D1     | D2 | D3 | D4 | D5 | D6 | D7 | ۲ | ь     | а |

| - | 1  | 0      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0     | 0 |

|   | 0  | 1      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0     | 1 |

|   | 0  | 0      | 1  | 0  | 0  | 0  | 0  | 0  | 0 | 1     | 0 |

|   | 0  | 0      | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 1     | 1 |

|   | 0  | 0      | 0  | 0  | 1  | 0  | 0  | 0  | 1 | 0     | 0 |

|   | 0  | 0      | 0  | 0  | 0  | 1  | 0  | 0  | 1 | 0     | 1 |

|   | 0  | 0      | 0  | 0  | 0  | 0  | 1  | 0  | 1 | 1     | 0 |

|   | 0  | 0      | 0  | 0  | 0  | 0  | 0  | 1  | 1 | 1     | 1 |

$$a = D_1 + D_3 + D_5 + D_7$$

$b = D_2 + D_3 + D_6 + D_7$

$c = D_4 + D_5 + D_6 + D_7$

Binary

Code

Gray

Code

$\mathbf{X}_{1}$

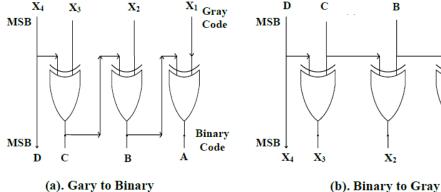

# **Binary to Gray / Gray to Binary Conversion:**

The gray code is widely used in many digital systems specially in shaft encoders and analog to digital conversion, but it is difficult to use the gray-code in arithmetic operations, since there are only one bit change between two consecutive gray code number, and it is unweighted code, and the XOR gate is the most suitable gate for this purpose as shown in Figure below:

$\mathbf{X}_2$